CMOS模擬集成電路設(shè)計(jì)基礎(chǔ)與HSPICE學(xué)習(xí)記錄

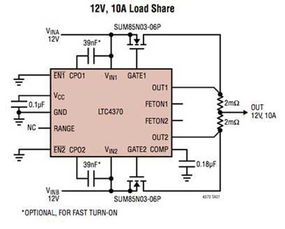

CMOS模擬集成電路設(shè)計(jì)是現(xiàn)代電子工程領(lǐng)域的重要分支,廣泛應(yīng)用于通信、電源管理和傳感器等系統(tǒng)中。艾倫(Allen)的課件為學(xué)習(xí)者提供了系統(tǒng)性的指導(dǎo),本文結(jié)合課件內(nèi)容,總結(jié)CMOS模擬集成電路設(shè)計(jì)的基礎(chǔ)知識(shí),并分享HSPICE工具的學(xué)習(xí)記錄與實(shí)踐經(jīng)驗(yàn)。

一、CMOS模擬集成電路基礎(chǔ)

CMOS技術(shù)是集成電路設(shè)計(jì)的核心,基于互補(bǔ)金屬氧化物半導(dǎo)體結(jié)構(gòu),具有低功耗、高集成度和抗干擾能力強(qiáng)等優(yōu)點(diǎn)。模擬電路設(shè)計(jì)涉及信號(hào)處理、放大、濾波等功能,與數(shù)字電路不同,模擬電路處理連續(xù)信號(hào),對(duì)噪聲、線性度和帶寬等參數(shù)要求嚴(yán)格。

基礎(chǔ)內(nèi)容包括:

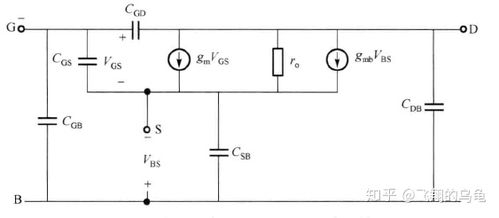

- MOS晶體管原理:理解NMOS和PMOS的工作機(jī)制,包括閾值電壓、跨導(dǎo)和輸出電阻等關(guān)鍵參數(shù)。

- 基本放大器結(jié)構(gòu):如共源放大器、共柵放大器和共漏放大器,分析其增益、輸入輸出阻抗和頻率響應(yīng)。

- 偏置電路設(shè)計(jì):確保晶體管工作在飽和區(qū),提高電路穩(wěn)定性。

- 反饋理論:應(yīng)用負(fù)反饋改善電路性能,如帶寬擴(kuò)展和失真降低。

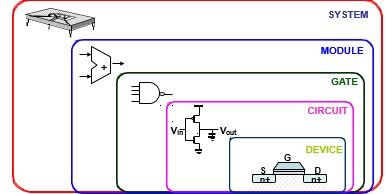

二、集成電路設(shè)計(jì)流程

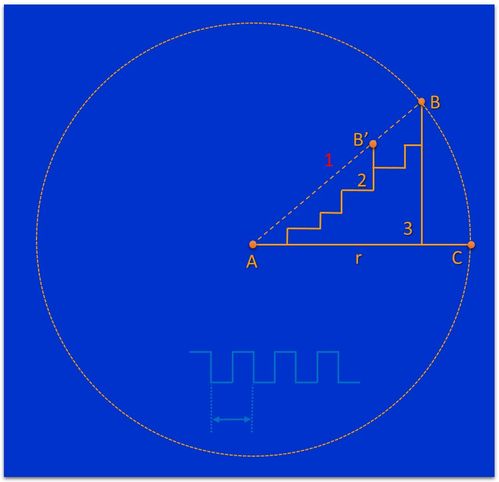

集成電路設(shè)計(jì)從系統(tǒng)規(guī)范開始,經(jīng)過電路設(shè)計(jì)、仿真、版圖繪制和驗(yàn)證等步驟。艾倫的課件強(qiáng)調(diào)了模擬設(shè)計(jì)的迭代性,需反復(fù)優(yōu)化以滿足性能指標(biāo)。設(shè)計(jì)過程中,需考慮工藝變化、溫度效應(yīng)和寄生參數(shù)的影響。

三、HSPICE學(xué)習(xí)記錄

HSPICE是行業(yè)標(biāo)準(zhǔn)的電路仿真工具,用于驗(yàn)證CMOS模擬電路設(shè)計(jì)。學(xué)習(xí)記錄包括:

- 基本語法:學(xué)習(xí)網(wǎng)表編寫,包括元件定義、模型調(diào)用和分析命令(如DC、AC和瞬態(tài)分析)。

- 仿真實(shí)踐:通過簡(jiǎn)單電路(如反相器或放大器)進(jìn)行仿真,觀察電壓、電流波形,并與理論計(jì)算對(duì)比。

- 參數(shù)優(yōu)化:利用HSPICE進(jìn)行蒙特卡洛分析或參數(shù)掃描,評(píng)估電路在工藝角下的魯棒性。

- 問題調(diào)試:識(shí)別仿真錯(cuò)誤,如收斂問題或模型不匹配,并學(xué)習(xí)解決方法。

掌握CMOS模擬集成電路基礎(chǔ)和HSPICE工具是設(shè)計(jì)高性能電路的關(guān)鍵。通過艾倫課件的系統(tǒng)學(xué)習(xí),結(jié)合實(shí)踐仿真,可以有效提升設(shè)計(jì)能力,為復(fù)雜集成電路項(xiàng)目打下堅(jiān)實(shí)基礎(chǔ)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.txwrkj.cn/product/39.html

更新時(shí)間:2026-01-08 02:48:37